With the recent growth of multi-core chips, scalibility of pure MPP LS-DYNA beyond 128 cores has shown degration due to several factors including latency and network communications. LSTC has recently developed a new code named “Hybrid LS-DYNA” that provides sustained scalibility for large number of cores and also yields digit-2-digit repeatibility when changing the number of cores per job. Both these offer tremendous advantages as we move forward to take advantage of multi-core chips. A surpise advantage that we recently saw is the ability to run IMPLICIT jobs in Hybrid LS-DYNA on comptuers with substantially less memory.

Hybrid MPP LS-DYNA is a very promising solver version that is very easy to run and set up. Below is a picture that illustrates the difference between pure MPP-LSDYNA and Hybrid LS-DYNA.

How Hybrid LS-DYNA Works [ click the image to enlarge]

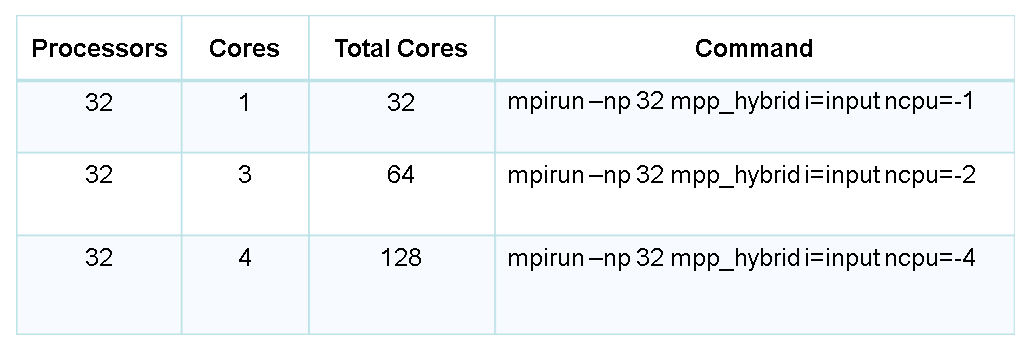

How to use Hybrid LS-DYNA. [click the image to enlarge]

Thanks to Dr. Jason Wang, whose presentation at the recently concluded Dynamore LS-DYNA Conference in Germany, was helpful for this post.